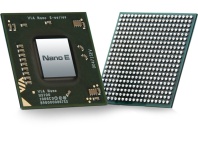

VIA Nano Dual-Core Preview

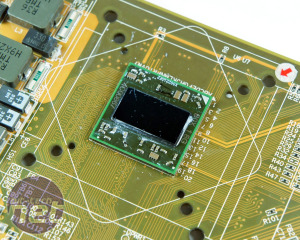

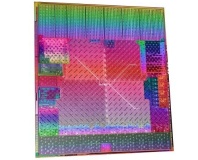

Manufacturer: VIAVIA's Nano CPU has just received its first major update: another one has been strapped to it. The aptly named Nano Dual-Core is actually VIA's first ever multi-core part, but even though we've got a reference board to test, things are still set to change before its introduction next year as the CPU gets respun from its existing 65nm down to 40nm, thanks to TSMC.

That node-and-a-half drop in manufacturing means the new dual-core hardware is expected to have the same 25W TDP as the current single-core products, retaining VIA's (and Centaur's) low power legacy.

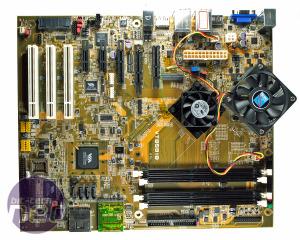

For those of you who have been making PCs for at least the last decade, no doubt you'll look at what VIA gave us and scratch your head. For the record, VIA isn't trying to 'bring back 2003' as a statement of fashionable industrial design, the board is purely made for internal testing only, which means aesthetic considerations are completely disregarded. You'll not be able to buy this piece of specific hardware, but VIA assures us it's entirely representative of the performance of what will eventually be on sale.

Oh, and we're the only European media with a sample, too!

While VIA was nondescript in every piece of information it sent us about this 'Nano Dual-Core', CPU-Z (and Wikipedia) informed us that each 1.8GHz CPU is a Nano L3050 with the following specs:

- 64KB L1 data cache and 64KB L1 instruction cache

- 1024KB L2 cache

- 500mW idle power (on current 65nm process but this will lower with the 40nm line)

- 20W TDP (on current 65nm process but will lower with the 40nm line)

- NanoBGA2 socket

In a brief chat to VIA when we picked up the board, it explained the design is about risk-reduction through keeping things as simple as possible. Neither CPU die is fundamentally changed, and the fact that VIA is dropping down a processing node will keep the team busy already (remember, Centaur Technology is levels of magnitude smaller than Intel and AMD). However, we already know the distinct limitations of this design.

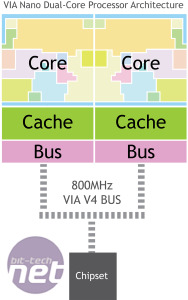

In a brief chat to VIA when we picked up the board, it explained the design is about risk-reduction through keeping things as simple as possible. Neither CPU die is fundamentally changed, and the fact that VIA is dropping down a processing node will keep the team busy already (remember, Centaur Technology is levels of magnitude smaller than Intel and AMD). However, we already know the distinct limitations of this design. To talk to each other, the CPU cores must use the C4 front side sus, sending signals out of the CPU package and then back in again. This adds a notable latency and causes much heavier bus traffic. The two large Level 2 caches might actually become a negative facet, as the only way for them to keep updated about one another is to communicate via this method. More cache means more data snooping. Modern CPUs have a large, on-chip Level 3 cache to do this now, or at least a level of on-die communication.

Even though VIA has played it safe with a known design method that works, compared to the days of the Pentium 4 or even quad-core Kentsfield, software is now much more multi-threaded; OSes are designed for much heavier multi-tasking and users demand more applications running at once than ever. All of which will cause a considerably greater strain on that 800MHz C4 (front side) bus.

This issue also affects VIA's PowerSaver, which dynamically clocks- and volts-down the CPU to save power. Unless the system is exclusively running a single thread, both cores will see some use pretty much constantly - Windows bounces threads across all available cores seemingly at random, for example.

In other situations or with other OSes, the active CPU is likely to wake up the idle one to check its status, and since the caches are on the same power domain as the rest of the core, the whole core is unlikely to sleep. While VIA may suggest its Nanos have a superb idle power, ultimately we expect the Nano Dual-Core to be either idle or fully awake, rather than spend much time in between these states.

On the plus side, the Nano L3050 has most of the latest microcode enhancements, including MMX, SSE, SSE2, SSE3, SSSE3, SSE4.1, x86-64, NX bit, x86 virtualization, as well as VIA's own PadLock (SHA, AES, RNG) hardware encryption. Only the more recent SSE 4.2 is missing, but that only counts for seven instructions.

MSI MPG Velox 100R Chassis Review

October 14 2021 | 15:04

Want to comment? Please log in.